兆芯 KX5000(8C8T) 标注

ZHAOXIN KX5000 FLOORPLAN

Image come from chipwiki and floor plan by me.图像来自于chipwiki并由我标注。

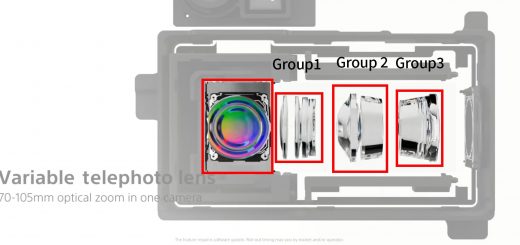

KX5000使用五道口架构(wudaokou)的8核心CPU构成,4个CPU组成一个集群(cluster)。使用HLMC的28nm工艺制造。一级指令缓存32KiB,一级数据缓存32KiB,二级缓存每个集群4MB。拥有双通道DDR4,PCI-E 3.0 *24(还有I/Oe*4)。

引用:上海华立微电子有限公司(HLMC)是一家中国代工厂。截至2018年,HLMC拥有55 nm,40 nm和28 nm 制程技术,每月可生产多达35,000个晶圆。

(https://en.wikichip.org/wiki/hlmc)

详细测量:

| die | size(mm^2) | process node | ||

| KX5000(8C8T) | diesize:187 | HLMC 28nm | ||

| Wudaokou Core | 2.509365932 | |||

| 1MB L2 | 2.456581685 | |||

| L1 Inst. | L1 Data | L2 | ||

| 32KiB | 32KiB | 1MB/core,4MB/Cluster | ||

| SRAM density(MB/mm^2) | Logic density | SRAM bitcell(μm^2) | ||

| HLMC 28nm | 0.407069712 | / | ≈0.292847357340759 |

HLMC的28nm的逻辑密度无法测量(,已知SRAM密度在 Intel10nm 工艺的23%的水平,逻辑密度的差距应该会比这更大。